Étape 6: La déclaration de Module

sélecteur d’entrée [0],

sélecteur d’entrée [1],

sortie conduit

);

le module est un mot-clé de Verilog. Pensez-y comme une déclaration de type ; en C++, nous pourrions avoir une déclaration de fonction de « Sub hello_world (< paramètres ici >) ». Notez les similitudes ?

Alors que Verilog ne retourne aucune valeur (comme une fonction C++ « void ») et n’est vraiment pas même une fonction, sa syntaxe est similaire et on peut encore penser du module comme une déclaration de type et « hello_world » comme nom (les noms en Verilog ne peut pas contenir des espaces). Bon code Verilog est « modulaire » et nous allons discuter de ce que cela signifie que plus tard (autres tutoriels sera bientôt disponibles sur mon site Web personnel et éventuellement Instructables).

Dans les parenthèses de la déclaration sont ce que nous pouvons assimiler comme notre liste de paramètres. Autrement dit, le module a une entrée appelée switch [0], une autre entrée appelée switch [1] et une sortie appelé conduit. d’entrée et de sortie sont essentiellement des types de variables. Il y a quelques bizarreries aux déclarations de module qui nous regarderons dans le module suivant.

Ne voyez-vous pas comment nous pourrions réduire notre entrée et sortie des déclarations de trois déclarations à deux ?

Astuce : Vous pouvez créer des tableaux (appelés bus) en Verilog !

Toutes les entrées et sorties sont déclarés, la liste des paramètres est fermée avec une parenthèse et un point-virgule ! Le point-virgule, tout comme en C++, marque la « fin » d’une déclaration. Une commodité de Verilog est la possibilité de fractionner les grandes déclarations telles que les instructions de la logique long en plusieurs lignes pour faciliter la lecture, tant que vous n’oubliez pas le point-virgule.

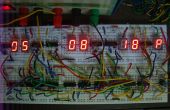

La photo montre le codage de couleur typique de déclaration d’un module.