Étape 12 : VM 3.0 : conception modulaire

Maintenant, vous devriez être capable de mettre en œuvre des fonctions logiques simples à l’aide d’opérateurs de base Verilog (|, &,...) et le faire exécuter sur votre carte FPGA. Si vous n’êtes pas tout à fait à ce stade, veuillez commencer par VM 2.0.

« VM 2.0 : mon premier Verilog Project », j’ai introduit le concept de « modules » et « modulaire » code ; maintenant, il y a quelques nuances de modules dont vous avez besoin de savoir pour être une utilisateur expérimenté "designer modulaire". Mais tout d’abord, nous devons en discuter « Ce qui est de conception modulaire? »

Si vous effectué l’exercice « hello_world », vous ont été introduits au mot-clé Verilog « module ». Chaque fichier source de Verilog contient uniquement une définition de module. Alors, comment pouvons-nous créer des projets complexes qui impliquent de nombreux modules plus petits ? Nous allons prendre l’exemple de la construction d’une minuterie contrôlée LED circuit. Qu’aurions-nous besoin de notre circuit pour faire une LED clignote toutes les secondes si un interrupteur est une logique un et nous n’avions qu’une horloge 50MHz ?

Briser ce que nous devons en trois catégories : entrées, sorties et les composants internes.

Entrées: sources de signaux physiques comme un oscillateur ("clock"), interrupteurs, boutons, ports de données, etc....

Sorties: sorties physiques qui seront pilotées par le circuit comme LEDs, ports de données, écrans, etc...

Composants internes: les composants qui prennent l’état des entrées pour générer une sortie désirée ; tous d'entre eux n’ont pas à être connectés aux ports de « haut niveau », mais finalement tout devrait « itinéraire ».

Relire ces classifications ; Il est vital que vous connaissez les différences ! Notez également les nouveaux mots de vocabulaire: « niveau supérieur » et « route ».

Pensez à ce que ces termes pourrait signifier... Je vais officiellement les définir dans une minute.

Assimiler ces trois types de composants à une équation algébrique, les entrées sont les variables indépendantes, les sorties sont les variables dépendantes et les composants internes représentent l’équation réelle. Se souvenant de cette analogie vous aidera à décider lorsque vous travaillez sur des projets, si un composant donné est un input, output ou composant interne.

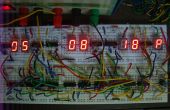

Dans le cas du circuit de clignotement de LED, voici ce que nous avons à un très haut niveau :

Entrées: horloge 50 MHz, interrupteur

Sorties: LED

Internals: un de 50 MHz à 1 Hz horloge diviseur, une seule porte et (parce que LED viendrait seulement on si les deux l’horloge divisée et l’interrupteur sont logique un)

Comment voulez-vous, à un très haut niveau (ce qui signifie que surtout « black boxes » représentent des composants plutôt que porte les patrons), bloc diagramme de ce circuit ? Rappelons que vous pouvez faire un diviseur d’horloge en connectant un certain nombre de D-Flip Flops (DFFs) ensemble avec des onduleurs.

Voir le diagramme ci-joint pour la réponse.

Défi : En réalité, nous aurions un bouton physique qui remettrait à zéro tous les DFFs dans le diviseur d’horloge. Peux-tu dessiner l’origine et la destination d’un bouton appelé « RST » sur ce schéma ?

Diagrammes de blocs comme celui-ci sont la première étape pour aider à que vous trouver une façon d’écrire un programme Verilog, comme toutes les cases dans le diagramme finira comme une instance d’un module dans votre code. Notez que nous avons un gros bloc qui contient un certain nombre de blocs plus petits ; Nous appelons cela le module « top ». Le module « top », c’est ce qui prend soin de relier tous les composants internes du circuit pour les sorties et les entrées physiques.

À l’intérieur de ce module particulier haut de la page sont deux choses : un diviseur d’horloge et d’une porte et. Mais remarquez que le bloc de diviseur d’horloge contient également un certain nombre de blocs plus petits (DFFs). Nous ne pas avoir à créer tous ces DFFs dans notre module supérieur ; Nous pouvons créer un module de diviseur d’horloge séparée qui contient tous les DFFs et créer une instance de ce diviseur d’horloge dans notre module supérieur.

Comme vous pourriez avoir deviné, nous devons également mettre un module forces de facto que nous pourrons instancier plusieurs fois dans le diviseur d’horloge. Cela nous permet seulement définissent le comportement d’un D-Flip Flop autrefois, puis instancier plusieurs instances de cette forces de facto. Tout ce que nous devons faire dans notre Verilog code est connecter à chaque instance de facto aux ports appropriés (c.-à-d. connecter ses entrées et sorties), mais plus sur l’instanciation de module plus tard.

Remarque : N’essayez pas de code de ce projet de LED clignotant tout de suite ; Il y a un peu plus de choses que nous devons couvrir.

Le point de ce module est de vous exposer à une conception modulaire ; vous voyez pourquoi j’appelle ces tutoriels « modules » ? Cette idée devrait être ancrée dans votre esprit que vous continuez d’apprentissage et à l’aide de Verilog.