Etape 11 : VM 2.0 : Port de Verilog et Types de fils

(module) hello_world

sélecteur d’entrée [0],

sélecteur d’entrée [1],

sortie conduit

);

Que signifient input et output dans ce contexte ? Ce sont des identificateurs qui indiquent au compilateur quel genre de « port » vous êtes en train de créer. En Verilog, nous traiterons les identificateurs suivants dans la déclaration de module :

entrée : un port d’entrée, type "fil" est supposé. Un port d’entrée ne peut être cédé que n’importe quelle valeur dans le module.

sortie : un port de sortie, type "fil" est supposé. Un fil de sortie peut être assigné une valeur à l’aide d’une instruction d’assignation ou avoir sa valeur déterminée indirectement par une instance d’un autre module. Un fil de sortie ne peut pas être assigné explicitement une valeur en toute logique conditionnelle (par exemple les déclarations de « if »).

sortie reg : un port de sortie de type "reg", abréviation de "s’inscrire". Une valeur indépendante des autres parties du circuit peut être attribuée à ce type de port (par ex. assignez-lui une logique « 1 ») et maintenir cette valeur jusqu'à ce que changé. Si vous changeront la valeur d’un port à partir d’un bloc « toujours » (un morceau de code qui s’exécute à toute modification de ses paramètres) vous devrez utiliser Règl.

En bref, un fil sert comme une forme de connecteur un point à un autre, comme d’un vrai mot source à une porte et et un reg peut créer sa propre source qui va vers une destination.

À l’intérieur d’un module, nous pouvons créer des fils internes et regs pour utiliser à l’intérieur du module. Cela est utile lorsque vous devez effectuer l’entrée d’une instance d’un module égal à la sortie de certains autre module instancié. Depuis un fil n’a pas son propre pilote, vous pouvez faire sa source la sortie d’un module et sa destination l’entrée d’une autre. Dans ce contexte, comment pensez-vous que vous déclareriez un fil ou reg pour utilisation à l’intérieur d’un module ?

fil my_wire ;

reg my_reg ;

Notez que nous n’avez pas à spécifier si le fil/reg est une entrée ou la sortie des fils internes et regs parce que pour lui Router correctement dans notre conception nous finalement lui donnera une source et une destination.

En Verilog, nous pouvons assigner un fil de sortie égal à un reg interne ou le fil. Cela nous permet de changer la valeur d’une sortie conditionnelle puisque si nous changeons le reg nous changeons aussi la sortie (n’oubliez pas que modifier directement la valeur sur une sortie est interdite).

Applicable à tous les ports susmentionnés, les fils et les regs sont ce qu’on appelle bus, ou, vecteurs (tableaux). Nous pouvons regrouper des signaux similaires à l’aide d’un bus. Dans le dernier exemple, j’ai posé la question de « Y a-t-il un moyen de définir seulement 2 ports pour trois total des intrants et des extrants? » À l’aide d’un bus, nous pouvons. Au lieu de déclarer "d’entrée switch0, switch1 d’entrée" nous pouvons simplement déclarer "entrée interrupteur [1:0]". Cela crée un bus deux bits appelé « switch ». Nous pouvons nous référer à des parties spécifiques de « switch » en utilisant l’opérateur [] comme dans "switch [0]". Bus sont très utiles en Verilog, car elle réduit la quantité de code, que nous devons produire.

Déclarer un bus à l’aide de la syntaxe suivante (« de type » désigne input, output, fil ou reg) :

< type > [< max indice > : < min index >] < nom bus >

Si vous déclarez un bus à l’intérieur d’un module, n’oubliez pas d’ajouter un point-virgule à la fin. Si vous déclarez qu'un bus dans la déclaration de module être sûr à virgule délimiter toutes vos définitions.

Quelles implications un bus a-t-elle sur votre fichier UCF ? Tous les composants du bus recevront un nom qui commence par le nom commun et est suivi par son index dans le bus. Donc "switch [1:0]" restera dans l’UCF comme deux entrées, « commutateur < 0 > » et « commutateur < 1 > ». N’oubliez pas d’utiliser les opérateurs de <> pour l’UCF !

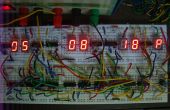

Sur la photo est maquette fils de raccordement ; vous n’aurez pas besoin de s’inquiéter de ceux sur la plupart des conseils conception FPGA comme ils ont construira stimuli tels que les commutateurs.