Étape 9: Préparer programmer votre carte FPGA

C’est vrai, l’UCF.

Alors que, comme mentionné précédemment, chaque fabricant de Conseil de conception numérique a des contraintes différentes pour différents conseils. Une contrainte de l’échantillon est la suivante :

NET « conduit » LOC = « M5 » ;

NET fait précéder chaque instruction, suivie du nom du net (en cours) et puis la contrainte réelle de la situation (également entre guillemets). Le nom peut être défini sur tout l’ingénieur désire (bien que les plus grands noms sont ceux qui ont le plus de signification en un minimum d’espace) et la contrainte d’emplacement indique où le « net » est physiquement connecté pour le FPGA. Un commentaire dans un UCF est indiqué différemment que dans le module Verilog ; dans un UCF, utiliser un « # » pour désigner un commentaire. Certains IDEs ont intégré dans les fonctionnalités qui vous permettent au code commentaire lot out en mettant en surbrillance le code désiré en appuyant sur la touche ou combinaison de touches dans l’IDE.

Donc si vous deviez passer par et créer un fichier UCF pour votre carte mère qui contient une contrainte pour chaque entrée et sortie, votre IDE serait en mesure de créer un flux binaire pour votre carte FPGA, conjointement avec le module de Verilog, que vous avez créé précédemment.

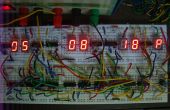

Le processus de programmation des différents conseils d’administration des FPGA varie, veuillez donc consulter votre fabricant pour obtenir des instructions spécifiques. La photo incluse est de ma carte FPGA plus mon remplacement de cavalier cent deux broches (temporaire et je ne recommande pas cela à moins que vous devez absolument continuer le débogage comme si j’avais à).

Note subsidiaire : Verilog modules sont stockés dans des fichiers ayant une extension bonano et UCF fichiers dans un format de .ucf. Les deux fichiers sont modifiables à l’aide de Notepad ou tout autre éditeur de texte (Wordpad tend à respecter les règles d’indentation mieux que le bloc-notes).