Étape 1: VM 1.0 : fond de Verilog

Mais sans n’importe quel contexte ou davantage la définition, c’est tous les Verilog signifiera pour vous. Langages de description matérielle (dans le contexte de l’ingénierie électrique) sont utilisés pour décrire formellement le comportement d’un circuit. Cela ne doit pas être une surprise étant donné le titre pas très créatif de « hardware description language » (qui est souvent plus simplement appelé HDL). Plusieurs HDLs existent, mais les deux langues les plus couramment rencontrées sont sans doute Verilog et VHDL (vous pouvez être tenté de raccourcir « Verilog HDL » à VHDL, mais ce sont deux langues distinctes, donc juste l’appeler Verilog!).

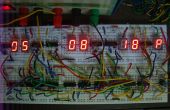

Nous pouvons utiliser des HDL comme Verilog pour beaucoup de choses ; C’est une utilisation plus importante, cependant, consiste à décrire sans ambiguïté un circuit particulier. Cela inclut décrivant ses entrées, sorties et comportement. Lorsqu’il est utilisé en conjonction avec une planche Field Programmable Gate Array (ou FPGA), nous pouvons créer une infinité de circuits juste en changeant sa description en Verilog ; un outil puissant de prototypage. Nous pouvons aussi utiliser Verilog sans un périphérique physique pour simuler des circuits et exécuter « saisons » sur notre HDL pour voir comment se comporterait le circuit devrions nous réellement construire (c.-à-d. a fait le circuit se comporte comme nous voulions?).

Sur la photo : Une partie de Verilog qui décrit une machine d’État. Cet apprêt court ne viendra pas n’importe où à proximité de ce code complex !