Étape 18 : VM 4.1 : le toujours bloquer

Si quelqu'un fait mention des mots « Verilog » et « Comportement » dans la même phrase, votre cerveau doit penser si tout va bien immédiatement « toujours bloquer ». Il n’est pas une vraie traduction entre un toujours bloc et quoi que ce soit dans une langue comme C/C++, mais le concept n’est pas difficile à comprendre. Mais si vous devez avoir une comparaison avec C/C++, un bloc est toujours comme un certain temps en boucle qui a condition du moment d’évaluer est un gâchis d’if déclarations.En un mot, un bloc est toujours une section de la logique de Verilog codé qui est évaluée, chaque fois que change de condition de déclencheur.

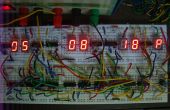

Que cela signifie-t-il ? Regardons un basic toujours bloc pour un circuit à deux entrées, sw0 et sw1.

toujours @ (sw0, sw1)

commencer

fin

Il n’y a aucun code du corps de ce bloc, mais nous allons ignorer que pour l’instant. Avis la ' ce produit « toujours » (« toujours » est un mot clé Verilog). Notez également l’instruction à l’intérieur des parenthèses: « sw0, sw1 ».

À l’aide d’une simple table de vérité, nous savons que pour deux entrées il y a un maximum de 4 Etats uniques les entrées pourraient être dans : deux logique haute, fois, logique faible et un haut un faible pour les deux entrées.

Le "toujours @ (sw0, sw1)" essentiellement dit « si à tout moment, toute entrée modifie son état (c.-à-d. changer de ligne sur la table de vérité) puis ré-évaluer le code suivant: ".

Ce ne serait pas trop simple pour écrire en C/C++, mais en Verilog, c’est aussi simple que cela. Un toujours bloc réévaluera le code dans sa portée (entre les instructions begin et end, suite à la déclaration « toujours ») quand on les déclencheurs (cette liste est appelée liste de sensibilité) soit à partir d’une logique un change à une logique de zéro ou d’une logique de zéro à une logique un. Pouvez vous pensez à un composant de circuit logique commun ou deux (ou un tas!) qui pourrait être mises en œuvre plus facilement dans une toujours bloquer?

L’exemple classique est le multiplexeur ou, mux. Lorsqu’une des entrées sélectionnez Modifier, le mux doit re-décider quelle entrée pour passer à la sortie. Le prochain quelques Modules tutoriel couvrir quel type de code « à l’intérieur », nous pouvons écrire un toujours bloquer.

Conseil du Pro : seul toujours bloc par Verilog module (fichier Kala). Ajuster la liste de sensibilité au lieu d’essayer de faire un autre bloc.

Indice (duplicate): vous ne pouvez définir des valeurs d’un reg dans une toujours bloquer, aucune assignation des valeurs pour les fils de type. Vous pouvez, cependant, plus tard affecter du fil égal à la valeur de la reg.