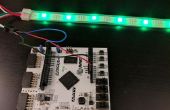

Étape 2: Création de la partie émettrice 1

L’émetteur a suivant des entrées et des sorties :

- entrée clk (une horloge 50 MHz)

- d’entrée reset (réinitialisation haute actif signal)

- transmission d’entrée (signal faible actif pour informer le module de chargement des nouvelles données)

- données d’entrée (valeur 8 bits pour envoyer transmettre signal)

- sortie Tx (le fil de transmettre sur)

Le

Tout d’abord, nous implémentons le diviseur d’horloge comme un compteur. À 50 MHz, une horloge de 9600 bauds peut être générée avec un compteur qui se réinitialise chaque 5207 de cycles d’horloge. Le bloc de mise à jour d’État avec levier de vitesses intégré ressemble à ceci :

always @ (posedge(clk))begin if (reset) begin state <= 0; counter <= 0; bitcounter <= 0; end else begin counter <= counter + 1; if (counter >= 5207) //baud of 9600 at 50MHz clk begin state <= nextstate; counter <= 0; if (load) rightshiftreg <= {1'b1, ^data, data, 1'b0}; if (clear) bitcounter <= 0; if (shift) begin rightshiftreg <= rightshiftreg >> 1; bitcounter <= bitcounter + 1; end end end end