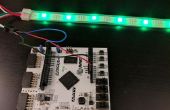

Étape 1: Planification de l’émetteur

L’émetteur nécessite trois blocs.

- Horloge de diviseuse - obtient le débit en bauds correct

- Registre à décalage - pousse les données de façon asynchrone à l’ordinateur

- State Machine - contrôles la Maj s’inscrire au rythme du diviseur d’horloge

Pour cela nous utilisons la conception du « paquet », comme illustré dans l’image ci-dessus

L’horloge de taux baud peut être généré avec :

divider = FPGA clock speed / desired baud rate

Pour cela, nous utiliserons 9600 bauds.

Il faudra un registre à décalage à utiliser comme un tampon FIFO (premier entré, premier sorti) pour les données avec un ordinateur d’État avec 2 États, Idle et la transmission.