Étape 3: Mise en page un onduleur à l’aide de P-cellules

1. créer une nouvelle vue de cellule de mise en page pour l’onduleur [Fig. 1]

A. mettre en disposition

B. cliquez sur OK

• La fenêtre mise en page s’ouvre avec un écran de mise en page vide

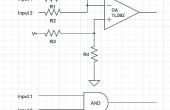

• Sur la gauche est la barre d’outils de calques dont vous choisirez quelle couche de conception vous travaillez actuellement. Le menu calques contrôle également quels calques peuvent être sélectionnés et qui sont visibles. [figure 2]

2. instancier un NMOS p-cellule, mise en page

• P-cellules sont pré-faites mises en page peuvent être modifiés pour répondre aux besoins du concepteur en changeant les paramètres du composant. Exemples de deux PMOS transistor p-cellules sont indiquées à la figure 3. La p-cellule de gauche a une largeur de 1,5 um et la p-cellule sur la droite a une largeur de 4.5um. [Fig. 3]

A. Sélectionnez créer ⇒Instance... ou une clé de succès du « i »

B. définir la bibliothèque « NCSU_TechLib_ami06 » [Fig. 4]

C. définir la cellule à "nmos" [Fig. 4]

D. définir l’affichage de "layout" [Fig. 4]

E. Vérifiez le nom du modèle est réglé sur « ami06N » [Fig. 4]

F. Définissez la largeur sur 1.5um [Fig. 4]

G. Placez la cellule dans la fenêtre de mise en page près de l’origine

3. disposition p-cellule Instantiate un PMOS

A. Sélectionnez créer ⇒Instance... ou une clé de succès du « i »

B. définir la bibliothèque « NCSU_TechLib_ami06 » (fig 5)

C. définir la cellule à "OMP" [figure 5]

D. définir l’affichage de "layout" (fig 5)

E. Vérifiez le nom du modèle est réglé sur « ami06P » (fig 5)

F. Définissez la largeur sur 4.5um [figure 5]

G. Placez la cellule dans la fenêtre de mise en page directement au-dessus de la cellule NMOS

• Les cellules NMOS et PMOS seront afficheront comme des représentations de niveau cellule (fig 6)

4. Appuyez sur la touche shift et la touche « F » simultanément pour que couche vue

• Les couches de la disposition deviendra visibles [fig 7]

• En appuyant simultanément sur la touche ctrl et la touche « F » retrouvera la vue le niveau de composants de la cellule et abstraire le schéma de configuration sous-jacent.

5. repositionner la cellule NMOS (fig 8)

• Centrer la porte (couche poly rouge) de silicium polycristallin des NMOS et PMOS uns avec les autres

A. Cliquez et maintenez enfoncé dans le centre de la cellule NMOS

B. faites glisser la cellule NMOS en position

6. Connectez le NMOS et PMOS Gates [figure 8]

A. Sélectionnez créer ⇒ ⇒ la forme Rectangle ou appuyez sur la touche « R »

B. Sélectionnez « poly » dans la barre d’outils de couches

C. dessiner un rectangle entre la porte de la NMOS et la porte de l’OMP

• Les polygones qui se chevauchent sur le même calque n’a aucun effet sur la mise en page.

7. Ajouter une connexion en vrac PMOS (fig 11)

A. Sélectionnez créer ⇒ Via...

B. Sélectionnez « PAEEN » pour la via un champ définition (fig 9)

C. Placez la PMOS en vrac connexion près le PMOS attaché au vert n-puits

• Le terminal vraquier est le n-bien que le PMOS est placé à l’intérieur.

8. Ajouter la connexion en vrac NMOS (fig 11)

A. Sélectionnez créer ⇒ Via...

B. Sélectionnez « M1_P » pour la via un champ définition [figure 10]

C. Placez la connexion en vrac NMOS gauche ou à droite du transistor NMOS

• Le terminal vraquier de la NMOS est le substrat p dopé.

9. Ajouter via pour relier l’entrée de la couche métallique pour les portes de silicium polycristallin (fig 13)

A. Sélectionnez créer ⇒ Via...

B. Sélectionnez « M1_POLY » pour le champ de définition (fig 12)

C. Placez la connexion en vrac NMOS gauche ou à droite du transistor NMOS

• L’entrée devrait commencer sur métal, il est donc facile d’acheminer de l’onduleur. La via relie le câblage d’entrée métallique pour les portes de silicium polycristallin.

10. fil l’entrée [figure 13]

A. Connectez l’entrée par la porte de silicium polycristallin

• Utiliser un rectangle de poly pour cette connexion

B. Raccorder l’entrée vers le bord gauche de la cellule.

• Utiliser métal 1 pour câbler l’entrée via et le bord gauche.

11. la sortie de fil (fig 13)

• La sortie va être câblée au bord à droite de la cellule.

• La sortie doit connecter la borne droite (vidange) de chaque transistor à la sortie.

12. les lignes d’alimentation de fil (fig 13)

• La DMV doit être établi comme un fil sur RADIOACTIVE1 dans la partie supérieure de la cellule.

• La DMV doit se connecter à la borne gauche (source) de la BDP et la majeure partie de l’OMP.

• Vss doivent être tracées comme un fil sur RADIOACTIVE1 en bas de la cellule

• Vss doivent se connecter à la borne gauche (source) de la NMOS et la majeure partie de la NMOS.

13. Ajouter broches d’alimentation [figure 14]

A. Sélectionnez créer ⇒ Pin...

B. définir des noms terminales à « La DMV Vss »

C. Sélectionnez « Entrées-sorties » comme type de I/O

D. Sélectionnez RADIOACTIVE1 dans la barre d’outils de calques

E. ajouter la DMV broche au fil d’alimentation haut de la page

F. Ajouter Vss broche au fil d’alimentation bas

14. Ajouter entrée Pin

• Pin devrait sera mis sur la couche de RADIOACTIVE1

• Broche possèdera de type « Input » I/O

15. Ajouter broche de sortie

• Pin devrait sera mis sur la couche de RADIOACTIVE1

• Broche possèdera de type « Sortie » e/s

La mise en page est maintenant prêt à être vérifiée.