Étape 4: Vérifier la mise en page

Test de la RDC :

1. exécuter la vérification de la RDC (fig 2)

A. Sélectionner vérifier ⇒ RDC...

B. cliquez sur OK

2. cocher RDC sortie en ligne de commande

• Presque toutes les mises en page rencontrera une fois erreur la première que République démocratique du Congo est couru

• La RDC signalera les erreurs dans la fenêtre de commande [Fig. 3]

• La RDC ne signalera aucune erreur trouvée en cas de réussite (fig 6)

3. identifier les erreurs éventuelles dans la mise en page

• Les erreurs sont signalées à l’aide de marqueurs blancs dans la fenêtre mise en page [Fig. 4]

• Les marqueurs peuvent s’expliquer en sélectionnant vérifier des marqueurs ⇒ ⇒ expliquer et puis en cliquant sur le marqueur. Une zone de texte s’affiche avec une brève explication de l’erreur. [figure 5]

4. corriger l’erreur

• Selon le type d’erreur, il y aura différentes solutions.

• La plupart des erreurs sont géométrique dans la nature et nécessitent la mise en page soit reconsidérée.

• Souvent déplacer un rectangle légèrement corrigera une erreur.

5. répéter la correction essai et erreur de RDC jusqu'à ce qu’il n’y a pas d’erreurs

• Une RDC réussie sera signalé comme 0 erreurs dans la fenêtre commande. (fig 6)

Test LVS :

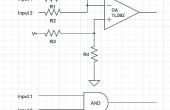

6. extraire le circuit [fig 7]

A. Sélectionner vérifier ⇒ extrait

B. cliquez sur OK

• Extraction estime les paramètres du circuit du schéma basé sur la mise en page

• Doit être remplie avant un test LVS peut commencer

• Le LVS compare en fait la vue extraite le schéma plutôt que la disposition réelle

7. Démarrer LVS (fig 8)

A. Sélectionner vérifier ⇒ LVS...

B. Sélectionnez vue schématique onduleur

C. Sélectionnez Affichage de l’onduleur extrait

D. cliquez sur exécuter

8. attendez que la VL pour achever

• Lorsque la VL est terminée une fenêtre s’ouvrira avec le statut de l’essai LVS. Si le windoe dit « Net-listes » correspondent à celui indique le schéma et la présentation sont simailar

• Si la fenêtre signale le LVS échec d’exécution de vérifier que les instructions à l’étape 7 ont été suivies correctement. Une erreur courante consiste à choisir la mise en page plutôt que la vue extraite.

9. examiner le fichier de sortie

A. Sélectionner vérifier ⇒ LVS...

B. Sélectionnez sortie [figure 8]

C. examiner le fichier de sortie pour les erreurs

• Cocher pour « Net-listes match »

• Rechercher les indicateurs d’erreur

• Le nombre d’appareils devraient être équivalentes dans le schéma et extrait des vues.

10. succès de document

• Prenez captures d’écran des deux tests de vérification pour le rapport de laboratoire