Étape 2: Créer le banc d’essai et de simuler le Circuit

Étant donné que le but de ce banc d’essai doit démontrer le glitch, au lieu de simuler toutes les transitions possibles d’entrée, nous sera élaborer une séquence d’entrée qui peut déclencher le glitch dans la sortie du circuit. En observant le circuit, il y a un chemin d’accès asymétrique entre l’entrée B et sortie X (c.-à-d., il y a deux chemins pour propager les modifications de B à la sortie avec différents retards). Si le Pépin se produira quand A et C sont constants et B bascule. Voici la description que nous allons créer dans le bloc initial de Verilog banc d’essai :

1 entier k = 0 ;

2

3 initiale commence

4 / / initialize entrées

5 = 0 ;

6 = 0 ;

7 C = 0 ;

8

9 / / attendre 100 ns pour reset global à la fin

10 / / Ajouter un stimulus ici

11

12 pour (k = 0; k < 4; k = k + 1)

13 commencer

14 (a, C) = k ;

15 # 5 = 1 ;

16 # 5 = 0 ;

17 #5 ;

fin 18

fin 19

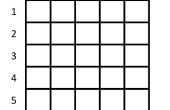

Simuler le banc d’essai dans le simulateur de Vivado, et vous obtiendrez l’affichage de forme d’onde, comme illustré dans la figure 2 ci-dessus. Le cercle rouge sur la forme d’onde spécifie le glitch. Alors, le Pépin arrive effectivement lorsque A est 1, C est 1 et B bascule de 1 à 0. La durée de la glitch est 1ns.