Étape 5: Construire un multiplicateur d’horloge 6 x

La chose est appelé « Horloge multiplicateur avec ligne de retard ». C’est sorte de simple. Retarder le signal d’horloge originale en période 1/6ème et faire un peu de logique avec ces signaux retardés des résultats dans une nouvelle horloge 6 fois plus vite que l’original.

Problème : Trouver une ligne à retard bien défini.

Solution : tâtonnements!!! J’ai trouvé les inverseurs CMOS 40098 d’avoir tour environ 150 ns retard de propagation. C’est assez proche de la 118ns de 708ns/6 désiré (44100 échantillons avec 16 bits et 2 canaux -> 44100 * 16 * 2 est 1,4112 MHz SCLK c’est un ~ 708ns période d’horloge)

Un peu plus ou moins de retard donnera toujours la même fréquence mais pas comme lisse, les hauts et les bas auront différentes longueurs.

Simulation

De projets antérieurs, je sais le Xilinx ISE, outils, qui sont librement disponibles pour effectuer la programmation FPGA et CPLD. Ils peuvent faire la simulation logique à l’aide du schéma, entrée de conception VHDL ou Verilog. Schéma pourrait être bon pour les débutants, mais c’est assez pénible de changer les choses en elle. Un langage de description matériel est beaucoup plus souple, mais bien sûr plus à apprendre.

En tout cas, la simulation est juste pour moi pour voir si l’idée fonctionne et pour vérifier quelle logique ferait l’affaire. Si vous êtes intéressé, vous pouvez trouver le projet de simulation attaché, décompressez-le et ouvrez le « ClockMult.xise » avec ISE. Une fois que vous l’avez fait jusqu'à maintenant vous pouvez brûler dans un CPLD, nullement, vous voulez amuser vintage ! :)

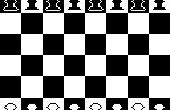

Le résultat peut être vu dans les images. L’horloge passe à travers les 5 40098 fois (6e onduleur inutilisé), à chaque sortie, vous voyez l’entrée précédente inversée et retardée. les signaux sont appelés clk_Xp et clk_Xn pour le positif et le négatif (un peu irritant ici parce que toutes les sorties de la 40098 sont appelés p même si ils basculer... Chaque sortie et l’horloge originale, traversent un deuxième inverseur (rapide) qui est un 74hc04 afin que chaque signal retardé est disponible comme un résultat positif (non inversé) et negative(inverted).

Après inversion, je prends deux signaux qui peuvent être AND'ed pour former une seule impulsion avec la longueur de 1/6ème de la période d’horloge.

Les impulsions sont ensuite OR'ed ensemble donnant l’horloge final 6 x.

L’AND est effectivement NAND parce que j’ai eu ICs 74hc00 (c’est une opération AND avec sortie inversée) rendant l’impulsion négative. Pour obtenir le même résultat, ceux-ci doit être AND'ed (N) au lieu de OR'ed. NAND ou et n’est pas grave parce que je n’aime pas sur la polarité des horloges final ou au henriq je peux simplement inverser à nouveau avec le 74hc00 ou 74hc04.

OK, cela fonctionne vraiment, en théorie;-)

Pour utiliser la nouvelle horloge 8,4672 MHz le Kenwood PCB doit être un peu changé. Le SM5807 s’exécute avec 16,9344 MHz, qui est deux fois plus que la 6xCLK mais la fiche technique dit qu’il aussi fonctionne avec le 8.4..MHz lorsque la broche 3 (CKSL) est reliée à « L » au lieu de 'H'. Bien sûr, le signal d’horloge originale doit être enlevé des broches 1. Notre jolie horloge nouvelle est ensuite injecté dans cette broche.

Nous allons sortir le PCB et changer la broche 3 de la SM5807 au GND et ajouter un pinheader pour l’horloge.

De la DP3010 de reparation il semble préférable d’enlever le cristal 16.9344 et ajouter la réglette à broches à la place (le pin face à broche 5 de la 7402) puis l’horloge va être inversé une fois de plus, n’est pas grave, juste simplifie la modification. Broche 2 et 3 de la SM5807 semblent non-connectés, donc j’ai juste ajouter un pont de broche 3 au sol. Qui devrait le faire. Assez simple.

fiche, prise...

Et ?

YYYYYYYYYYYYEEEEEEEEEESSSSSSSSSSSSS!!!

Œuvres, pas de clics plus, cool.

C’était amusant:-)

Aucun inconvénients ?

Eh bien la maquette n’est pas la pièce la plus fiable de tech, touch et là rend le tout fou. Peut-être le CPLD sur un PCB soudé simple n’est pas une si mauvaise idée après tout.