EE214

Projet 6: Un système de Communication Simple

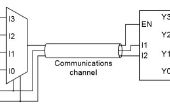

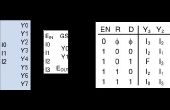

Dans ce projet, vous concevrez un mux 4 à 1 et un décodeur avec un signal d'activation comme un « de-mux » à mettre en place un émetteur de données série simple. Mux tant de-mux seront exécutés dans deux fichiers de Verilog pour réutilisation future.

Projet 7: Simuler Glitch et retard dans les Circuits combinatoires

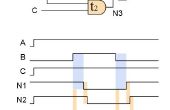

Dans ce projet, nous allons examiner le retard pris dans les circuits combinatoires. Nous allons dire le simulateur du retard de chaque porte en Verilog et simuler les circuits pour voir comment le retard peut affecter le comportement d'un circuit co

Projet 2.1 : Mettre en place un Circuit logique Simple

Dans ce projet, vous téléchargerez un fichier bit votre planche afin de configurer le FPGA avec quatre différents circuits de logique. Les circuits utilisent des commutateurs et des boutons pour les entrées et les LEDs pour les sorties. Vous devez so

Projet 3.1 : Majorité des 5

Comment pouvez-vous trouver une majorité des voix si chacune des cinq électeurs possède un interrupteur de voter oui ou non ? La logique est assez simple et sera utilisée dans ce projet. N'importe quel moment il y a trois ou plus des cinq qui vote ou

Projet 5: Multiplexeur, décodeur, encodeur et Shifter

Dans ce projet, vous concevrez un multiplexeur, un décodeur, un encodeur et un levier de vitesses à l'aide de Verilog HDL. Au lieu de construire le circuit en utilisant les opérateurs logiques, vous allez apprendre à décrire un circuit sur le plan co