Étape 4: Créer un Wrapper comme le Module de niveau supérieur

Dans cette étape, nous allons créer le module de niveau supérieur, dans lequel un multiplexeur et un de-mux seront instanciés et correctement connectés pour former un temps simple système de communication de multiplexage. Le diagramme système est illustré à la Fig. 3 ci-dessus.

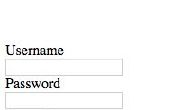

Dans le schéma-bloc, les ports d’entrée/sortie du wrapper de module est en vert ; les ports d’entrée/sortie du module mux et demux est affiché en italique noir ; et le fil interne du module emballage est en violet.

Dans le projet, créez un nouveau fichier de module de Verilog nommé wrapper avec entrées de 4 données (I3, I2, I1, I0), 2 Sélectionnez les entrées (S1, S0) et quatre sorties (Y3, Y2, Y1, Y0).

(wrapper) 1 module

2 I0, I1, I2, I3, S0, S1, Y0, Y1, Y2, Y3

3) ;

4

5 entrée I3 I2 I1, I0, S1, S0 ;

6 sortie Y0, Y1, Y2, Y3 ;

7

8 / / Description structurelle du wrapper

9

10 endmodule

Déclarer surlabasedesdonnéesdufabricantduballast fil interne après la déclaration d’entrée et de sortie.

1 fil surlabasedesdonnéesdufabricantduballast ;

Instancier le de-mux (nommé output_demux) et les fils de raccordement dans le wrapper pour les ports d’e/s de la de-mux.

1 () output_demux demux

4 h En(sdata),

3. I1(S1),

4. I0(S0),

5. Y0(Y0),

6. Y1(Y1),

7. Y2(Y2),

8. Y3(Y3)

9) ;

Tout mettre ensemble. Le niveau supérieur Verilog module auront lieu comme suit :

(wrapper) 1 module

2 I0, I1, I2, I3, S0, S1, Y0, Y1, Y2, Y3

3) ;

4

5 entrée I3 I2 I1, I0, S1, S0 ;

6 sortie Y0, Y1, Y2, Y3 ;

7

8 / / Description structurelle du wrapper

fil 9 surlabasedesdonnéesdufabricantduballast ;

10

(input_mux) 11 mux

12. I3(I3),

13. I2(I2),

14. I1(I1),

15. I0(I0),

16. S1(S1),

17. S0(S0),

18. Y(sdata)

19) ;

20

(output_demux) 21 demux

22. En(sdata),

23. I1(S1),

24. I0(S0),

25. Y0(Y0),

26. Y1(Y1),

27. Y2(Y2),

28. Y3(Y3)

29) ;

30

31 endmodule

Créez un fichier XDC comme suit :

-I3 à SW3 ; I2 à SW2, I1 à SW1, I0 à SW0

-Y3 à DEL3 ; Y2 de LED2, Y1 à LED1, Y0 à LED0

-S1 à BTN1, S0 à BTN0