Étape 15 : Circuit 1 de mettre en oeuvre en Verilog HDL

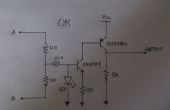

Construire et mettre en œuvre l’équation logique pour Circuit 1 selon la table de vérité. Nous construirons l’équation logique sous forme de SOP pour démonstration. Dans le Circuit 1, nous avons deux lignes (ligne deuxième et troisième rangée) qui montre un « 1 » dans la sortie. Il faut donc une porte d’OR avec deux entrées qui génèrent la sortie et les deux portes et de 2 entrées qui prévoient l’entrée de la porte d’OR. Dans la deuxième rangée, SW0 d’entrée indique un « 1 » et d’entrée SW1 indique « 0 ». Alors SW0 est connecté à l’entrée de la première porte et et SW1 est inversée avant de brancher la seconde entrée de la porte et, comme indiqué dans le premier terme de produit dans l’équation. Dans la troisième rangée, entrée SW0 montre un « 0 » et SW1 d’entrée indique un « 1 ». Alors SW0 est inversée avant de brancher à l’entrée de la seconde porte et et SW1 est relié directement à la deuxième entrée de la porte et, comme le montre le second terme du produit dans l’équation. La sortie LD0 est la somme de ces termes de deux produits.

En Verilog HDL, ce circuit est implémenté comme indiqué ci-dessus.