Étape 5: Porte NAND

![]()

![]()

![]()

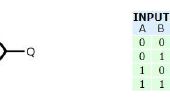

Porte A NAND est également dénommé une porte niée et. C’est le contraire ou l’inverse d’une simple porte et. Avec l’entrée et que la sortie a été contraint à une logique haut (1) uniquement lorsque les deux entrées lorsque forcé à logique haut (1), mais avec une NAND gate la sortie est obligé de logique faible (0) lorsque les deux entrées sont obligées de logique haut (1) et la sortie est forcée pour logique haut (1) dans toutes les autres situations.

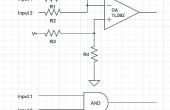

Pour la logique NAND, les transistors sont en série, mais la sortie est au-dessus d’eux. La sortie est élevée à moins que des A et B entrées sont élevées, auquel cas la sortie est descendue près de terre potentielle.

Dans le simulateur, j’ai utilisé accidentellement une résistance de 200 ohms, mais en réalité vous devez utiliser environ 1K ou quelque chose comme ça.