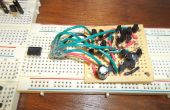

Étape 2: Circuit Design

Dans la conception de ces deux OR et pas la porte, j’ai utilisé un transistor PNP à la sortie. Basé sur l’expérience, un transistor PNP a une Vce(sat) inférieure ou une tension de saturation collecteur-émetteur minimale pour une utilisation à, devinez quoi... la région saturée. Parfois elle atteint 0, 5V ou même aussi faibles que 0,05 mV Lorsque vous augmentez considérablement le Vbe du transistor juste en dessous de sa valeur maximale avant IT BLOWS UP. Mais pourquoi voulons-nous une plus petite quantité Vce(sat) ? Pour que la sortie soit assez proche de Vcc suivant lesdits critères plus tôt.

Dans le circuit schématique, Vbe des transistors PNP sortie sont mesuré à plus de 0.73V assez pour faire fonctionner à la région saturée. Vous pouvez cependant modifier la conception de pousser plus loin et avoir un Vbe de plus de 1V. Juste de faire attention à ne pas lui fournir plus de 6V depuis si je ne me trompe pas, 6V est le maximum autorisé de Vbe à exploiter le transistor (cocher feuille de données).

En raison de la configuration PNP à la sortie, lorsque le transistor est dans la région de la coupure, la sortie va également aussi bas que 0 v en raison de la résistance de 5 K raccordée à la terre, encore une fois, après lesdits critères.

Maintenant qu’en est-il du chargement effet ? Eh bien, en raison de la configuration à la sortie du transistor, effet de chargement serait négligeable et quelle que soit la charge de sortie, la tension de sortie serait toujours constante puisqu’il ne change pas le fait que nous forçons le transistor de sortie pour fonctionner à saturation/coupure-off et il dépend principalement de la valeur de ses Vbe, pas la résistance de sortie. De cette façon nous pouvons monter en cascade n’importe quelle combinaison des deux portes logique sans aucune compensation sur les bornes d’entrée et de sortie de chaque étape/gate.