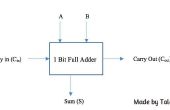

Le but de ces directives est de créer un additionneur 4 bits dans Quartus II. Un additionneur 4 bits est un modèle simple d’une calculatrice. Il faut deux nombres de 4 bits, ce qui nous permet de prendre des nombres 0 à 15, mais nous allons utiliser les chiffres 0-9. Les nombres sont alors additionnées. Le circuit est fait de Quartus II et puis est programmé sur un champ Gate Array (FPGA Programmable) qui permet le circuit à utiliser.

Ce projet est destiné à être pour le plaisir ou pourrait être un projet final pour une classe, mais est surtout de se familiariser avec les circuits logiques. Ce projet fera plus de sens si vous avez déjà pris ou prenez actuellement une classe de logique numérique et avez une compréhension de base de portes logiques. Quelques commandes de base de Quartus sont également couverts si vous ne l’avez jamais utilisé.

Le FPGA a boutons, interrupteurs, voyants et numéro affiche pour accueillir la plupart des circuits. Quartus 2 peut être acheté pour près de $ 3 000-$ 4 000 ; Bien que, l’édition web du logiciel est gratuite, mais nécessite l’achat d’un FPGA. J’ai trouvé des FPGA en ligne pour environ 200 $. J’ai utilisé le logiciel campus, donc je n’ai pas acheter n’importe quel équipement. Il m’a fallu 6 heures pour terminer l’additionneur à partir de zéro ma première fois. Mes espoirs avec ces instructions sont pour vous d’être en mesure d’achever l’additionneur 4 bits en moins de 5 heures. Compléter ce circuit vous amènera à une meilleure compréhension et réalisation avec sa complexité.

Remarque : Les photos au début de chaque spectacle de page donné étapes dans le processus. Ils sont à éviter toute confusion